# **Making the Java Memory Model Safe**

ANDREAS LOCHBIHLER, Karlsruhe Institute of Technology

This work presents a machine-checked formalisation of the Java memory model and connects it to an operational semantics for Java and Java bytecode. For the whole model, I prove the data race freedom guarantee and type safety. The model extends previous formalisations by dynamic memory allocation, thread spawns and joins, infinite executions, the wait-notify mechanism, and thread interruption, all of which interact in subtle ways with the memory model. The formalisation resulted in numerous clarifications of and fixes to the existing JMM specification.

Categories and Subject Descriptors: D.3.1 [**Programming Languages**]: Formal Definitions and Theory— Semantics; F.3.2 [**Logics and Meaning of Programs**]: Semantics of Programming Languages—Operational Semantics; D.3.3 [**Programming Languages**]: Language Constructs and Features—Concurrent Programming Structures

General Terms: Languages, Theory

Additional Key Words and Phrases: data race freedom, Java memory model, operational semantics, type safety

### **ACM Reference Format:**

Lochbihler A. YYYY Making the Java Memory Model Safe ACM Trans. Program. Lang. Syst. V, N, Article A (January YYYY), 65 pages.

#### 1. INTRODUCTION

Type safety and the Java security architecture distinguish the Java programming language from other mainstream programming languages like C and C++. Another distinctive feature of Java is its built-in support for multithreading and its memory model for executing threads in parallel [Gosling et al. 2005, §17]. To enable optimisations in compilers and hardware, the Java memory model (JMM) allows more behaviours than interleaving semantics. It therefore non-trivially interacts with type safety and Java's security guarantees. Although this is well-known [Gosling et al. 2005; Pugh 2000], their combination has never been considered formally.

Here, I present a machine-checked model of Java and the JMM called JinjaThreads for both Java source code and bytecode, and investigate the impact of the Java memory model on type safety and Java's security guarantees. In particular, my contributions are the following:

First, I present a *unified formalisation* of the axiomatic JMM based on the operational JinjaThreads semantics for Java source code and bytecode (§2). This provides the first rigorous link between a Java and the JMM, which several authors have cri-

Preliminary versions of §1.1, §2.2 to §2.4, §2.7, §3, and §7 have appeared in [Lochbihler 2012a]. The author's PhD thesis [Lochbihler 2012b] contains preliminary versions of the same sections plus §4 and §5.1. This work has been partially supported by the Deutsche Forschungsgemeinschaft under grants Sn11/10-1,2. Author's address: A. Lochbihler, Institute of Information Security, ETH Zurich, 8092 Zurich, Switzerland. Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org.

© YYYY ACM 0164-0925/YYYY/01-ARTA \$15.00

DOI 10.1145/0000000.0000000 http://doi.acm.org/10.1145/0000000.0000000

A:2 Andreas Lochbihler

tised as missing [Aspinall and Ševčík 2007a; Cenciarelli et al. 2007; Huisman and Petri 2007]. My model of Java builds on 15 years of formalised Java semantics, from Nipkow and von Oheimb [1998] to Lochbihler [2012b]. It features dynamic memory allocation, thread spawns and joins, the wait-notify mechanism, interruption, and infinite executions. Each of these is well-understood and has been formalised before, e.g., [Liu and Moore 2003; Petri and Huisman 2008; Farzan et al. 2004a; 2004b]. But their combination with the memory model is novel and results in subtle interactions, which previous JMM formalisations have missed [Aspinall and Ševčík 2007a; Cenciarelli et al. 2007; Huisman and Petri 2007; Boyland 2009]. I illustrate these cases with new examples and show how to deal with them. Dynamic allocation and the special treatment of memory initialisation in the JMM are the main complication in the definitions and proofs. In particular, it does not suffice to consider only finite (prefixes of infinite) executions. Coinductive definitions and proofs fortunately deal with terminating and infinite executions uniformly (§1.2 introduces the relevant concepts).

Second, I clarify the existing JMM specification and fix it where it is inadequate (see §6 for a summary). This draws on two sources: On the one hand, carefully working through all the subtle interactions between Java and the JMM exposes unclarities and inconsistencies. On the other hand, the safety properties below hold only after some fixes derived from analysing failed proof attempts.

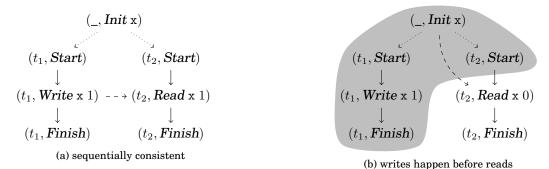

Third, I formally prove the *data race freedom (DRF) guarantee* (§3): For correctly synchronised programs, the JMM guarantees interleaving semantics, which is also known as sequential consistency (SC) [Lamport 1979].<sup>1</sup> In other words: If a programmer makes sure that there are no data races (e.g., by using locks), then she can forget about the JMM and assume interleaving semantics.

In this work, I resolve the inconsistencies with initialisations of memory allocations in previous proofs [Manson et al. 2005; Huisman and Petri 2007]. By fixing the definition of data race [Jacobs 2005], I strengthen the formal guarantee such that it now holds also for programs that synchronise via volatiles, see Figs. 4 and 22 for examples. Moreover, I bridge the gap between the axiomatic style of the JMM and the operational JinjaThreads semantics. To that end, I identify the assumptions of the proof about the single-threaded semantics and discharge them using the above link. In particular, I explicitly construct sequentially consistent executions for a given prefix by corecursion. Hence, I am the first to prove the DRF guarantee unconditionally.

Forth, I prove that the JMM allows every execution that interleaving semantics produces (§4). This is the converse of the DRF guarantee, but also holds for programs with data races. Hence, despite its technical complexity, the JMM specification is consistent in that it defines some behaviour for every program, not just for correctly synchronised ones. This is non-trivial in the presence of data races and, to my knowledge, has not been proven before.

Fifth, I show *type safety* (§5), independent of correct synchronisation. Unfortunately, the axiomatic nature of the JMM is not suited for standard proofs using subject reduction, as Goto et al. [2012] have observed. Direct proofs must deal with reads retrieving type-incorrect values from the shared heap, because the JMM matches reads with writes a posteriori. To avoid the induced complications, I rather follow a two-step approach. I prove that each value read from memory during any legal execution is of the expected type (§5.2). Hence, the usual progress and preservation theorems [Wright and Felleisen 1994] may assume type-correct reads and, therefore, do not depend on

<sup>&</sup>lt;sup>1</sup>A data race occurs when two confliciting accesses may happen concurrently, i.e., without synchronisation in between; two accesses to the same (non-volatile) location conflict if they originate from different threads and at least one writes. A program is correctly synchronised iff no SC execution contains a data race.

the memory model. In fact, I reuse the existing type-safety proofs from previous work [Lochbihler 2008] that were ignorant of the memory model.

Surprisingly, a weakness in the JMM specification allows pointer forgery. This breaks type safety (§5.1) when the JMM is combined with the standard run-time type system for Java [Drossopoulou and Eisenbach 1999], which stores type information inside the objects on the heap. I show that encoding type information directly in the references themselves rescues type safety. Thus, Java with the JMM is type safe and allows pointer forgery at the same time, which normally exclude each other. However, pointer forgery allows behaviours that break Java's security architecture (§5.4), independent of how type information is stored. This shows that the JMM really needs to be revised in some form; yet, it is unclear whether a quick fix is possible at all, as my examples suggest that the flaw is inherent to the committing style of the JMM.

Sixth, the JMM is very technical and subtle, and so are the proofs; machine support is therefore essential – as a series of false claims about the JMM and their subsequent disproof demonstrates [Manson et al. 2005; Cenciarelli et al. 2007; Ševčík and Aspinall 2008; Torlak et al. 2010]. All my definitions and proofs have been checked mechanically by the proof assistant Isabelle/HOL [Nipkow et al. 2002]. But this is not just the mechanisation. I have designed the proof structure carefully to be as abstract as possible and reasonable: an interface of signatures and assumptions connects the concurrent semantics and proofs to the single-threaded ones. This yields a tractable concurrency model that does do not rely on the specifics of the concrete language. I demonstrate this by specialising the results to both Java source code and bytecode, but they apply to other languages and memory models as well. For example, Boehm and Adve's proof [2008] of the DRF guarantee for C++ also postulates sequentially consistent completions; my corecursive construction fits there, too. Hence, the challenging proofs about the concurrent semantics have to be done just once. Moreover, the assumptions on the single-threaded semantics have the usual format of invariants and preservation. Thus, ordinary inductions suffice. This is a major improvement over the axiomatic style of memory model specifications.

The presentation focuses on the relevant parts of the concurrent semantics, omits most of the single-threaded semantics, and illustrates the subtleties rather with examples than formal definitions. A detailled description of the technical details can be found in the author's PhD thesis [Lochbihler 2012b]; the formalisation with all the ugly details of mechanised proofs is available online in the Archive of Formal Proofs [Lochbihler 2007]. In §1.1, I informally explain the JMM; the appendix summarises Java's concurrency primitives.

Throughout the article, I contrast my approach with others' and discuss the advantages and drawbacks using examples. Moreover, I thoroughly review the existing literature on the JMM (§7). Hence, this work can serve as a reference of the JMM and its relation to the semantics, as it collects the strengths and weaknesses of the current JMM. For the next revision of the JMM, this will be a valuable resource of what must not be missed.

#### 1.1. Informal Introduction to the Java Memory Model

The Java memory model [Manson et al. 2005; Gosling et al. 2005, §17.4] specifies how shared memory behaves under concurrent accesses. This section sketches the main ideas behind the JMM.

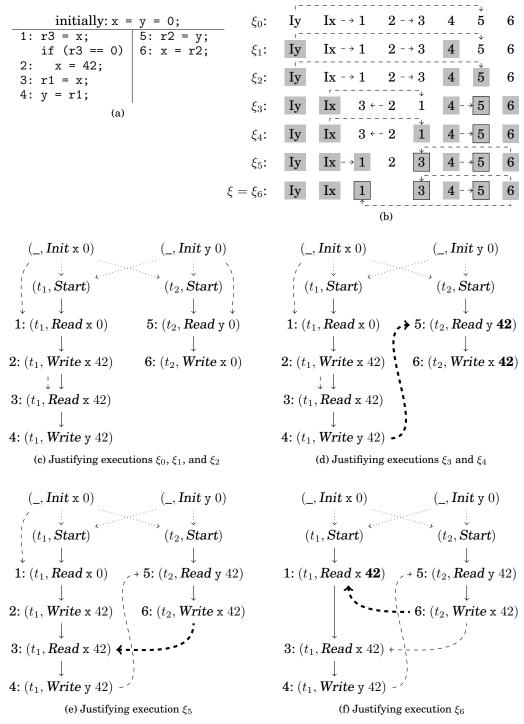

1.1.1. Motivation. The program in Fig. 1a has two threads, each of which reads one of C's static fields x and y into a local variable and subsequently sets the other to 1. Figure 1b shows all possible interleavings of the two threads, and for each schedule, the final values for the threads' local variables r1 and r2. All these schedules assume

A:4 Andreas Lochbihler

Fig. 1: Program with two threads (a) and all of its sequentially consistent schedules (b)

sequential consistency (SC) [Lamport 1979], which is considered the most intuitive memory model [Hill 1998]: There is a global notion of time, one thread executes at a time, and every write to a memory location immediately becomes visible to all threads. In particular, the result  $r_1 == r_2 == 1$  is impossible under SC as the following argument shows. Suppose it was possible. Then, l. 1 executes after l. 4 and l. 3 after l. 2. As l. 1 and l. 3 literally precede l. 2 and l. 4, respectively, one obtains the contradiction that l. 1 executes after l. 4 after l. 3 after l. 2 after l. 1.

For efficiency reasons, modern hardware implements memory models that are weaker than SC to allow for local caches and optimisations [Adve and Gharachorloo 1996; Sorin et al. 2011]. For example, if the threads t1 and t2 execute on different cores of a processor, the reads in ll. 1 and 3 might still be waiting for memory to return the values, when the writes in ll. 2 and 4 execute. If intra-processor cache communication is faster than memory, both pending reads may return the written values, i.e., 1. This results in r1 == r2 == 1, which is not possible under SC. Similarly, compiler optimisations might reorder the independent statements in each thread. Then, r1 == r2 == 1 is possible for the transformed program even under SC. Therefore, a correct implementation of SC must take extra precautions: As the code does not provide any clues about how threads communicate via shared memory, it must either conservatively disable such optimisations in *all* code or laboriously analyse whether they are allowed [Sura et al. 2005]. To avoid the ensuing slow-down, the JMM relaxes SC and allows the outcome r1 == r2 == 1 in the example.

Nevertheless, the JMM provides the intuitive SC semantics under additional assumptions – known as the data-race freedom guarantee [Adve and Hill 1990]. Two accesses to the same location *conflict* if

- (1) they originate from different threads,

- (2) at least one is a write, and

- (3) the location is not explicitly declared as volatile.

A *data race* occurs if two conflicting accesses to a location may happen concurrently, i.e., without synchronisation in between. If the program contains no data races, the JMM promises that it behaves like under SC. In other words: If a programmer protects all accesses to shared data via locks or declares the fields as volatile, she can forget about the JMM and assume interleaving semantics, i.e., SC.

In the above example, there are two data races: the write of c.y in l. 2 races with the read in l. 3 and similarly l. 4 and l. 1 for c.x, i.e., the DRF guarantee does not apply. To eliminate these data races, one can use Java's synchronisation mechanisms, e.g., wrapping every line in its own synchronized block on c's class object. Alternatively,

one can declare C's static fields x and y as volatile, because accesses to such fields never conflict.<sup>2</sup>

- 1.1.2. Components of a JMM Execution. Since the JMM must ensure that compilers can implement Java on a variety of hardware with different MMs efficiently, it reduces concrete thread operations to events, which are called inter-thread actions in JMM terminology:

- reading (*Read*) from, writing (*Write*) to and initialising (*Alloc*)<sup>3</sup> a location on the heap,

- locking (*Lock*) and unlocking (*Unlock*) a monitor,

- interrupting (*Intr*) a thread and observing that it has been interrupted (*Intrd*),<sup>4</sup>

- spawning (Spawn) of and joining (Join) on a thread, and

- external actions (IO) for input and output, for example, and

- Start and Finish to mark mark the start and termination of a thread, respectively.

This way, the JMM is independent from syntax and implementation techniques. It nevertheless gets a global view on how a given program works algorithmically and on how its threads interact, and uses this to determine the set of legal behaviours.

A JMM execution consists of a sequence of such events for each thread, three orders on these events (program order, happens-before order, and synchronisation order), and a function that assigns writes to reads.

*Program order* (notation  $\leq_{po}$ ) totally orders the events of each thread according to their occurrence in the thread's sequence, but does not relate events from different threads.

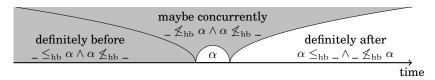

The (partial) happens-before order  $\leq_{\mathrm{hb}}$  provides a notion of time relative to a given event  $\alpha$ . As Fig. 2 illustrates, it partitions the other events of the execution into three groups: those that must have happened before it ( $_{\leq_{\mathrm{hb}}}$   $\alpha \wedge \alpha \not\leq_{\mathrm{hb}}$   $_{\leq_{\mathrm{hb}}}$ ), those that must happen after it ( $\alpha \leq_{\mathrm{hb}} - \wedge _{\leq_{\mathrm{hb}}} \alpha$ ), and those that may happen concurrently ( $_{\leq_{\mathrm{hb}}} \alpha \wedge \alpha \not\leq_{\mathrm{hb}} _{\leq_{\mathrm{hb}}}$ ). Since  $\alpha$ 's thread knows that all of its events prior to  $\alpha$  must have happened and all posterior to  $\alpha$  must not yet have happened,  $\leq_{\mathrm{hb}}$  always includes  $\leq_{\mathrm{po}}$ . Additionally, synchronisation events, which are all events except for external actions and reads from and writes to non-volatile locations, introduce happens-before relationships between events of different threads. For example, spawning a thread  $t_1$  (event  $s_{1}$ ) synchronises with  $s_{2}$ 0 synchronises with  $s_{3}$ 1 start event  $s_{4}$ 2. In combination with program order, all events of the spawning thread before the spawning happen before any of  $s_{2}$ 3 events. Similarly, a write to a volatile location synchronises with a read that sees it, because the reading thread then knows that the write must have occurred before. The

$<sup>^2</sup>$ When a thread reads from a volatile field, it synchronises with all other threads that have written previously to that field. Hence, the reading thread can be sure that everything that should have happened in the other threads prior to their writes in fact has happened prior to its read. For the formal semantics, see §2.4.  $^3$ Technically, the JMM defines initialisation actions each of which initialises only a single location. JinjaThreads uses one event per memory allocation that initialises all members of the allocated object or array. This way, allocation events keep track of allocated addresses whereas JMM initialisation actions would not if the allocated object or array contains no members, e.g., an array of length 0. The special treatment of allocations in the JMM (see below) ensures that this deviation does not matter semantically. For clarity, I write  $Init \times for$  initialising global variables in examples. Formally, a bootstrapping thread initialises such variables with allocations as explained in §2.3.

$<sup>^4</sup>$ The JMM list of inter-thread actions does not mention Intr and Intrd [Gosling et al. 2005,  $\S17.4.2$ ], but the definition of synchronisation points [Gosling et al. 2005,  $\S17.4.4$ ] includes interrupts and observing an interruption. My events Intr and Intrd model these two points.

$<sup>^5</sup>$ For technical reasons, the JMM's happens-before order  $\leq_{\mathrm{hb}}$  is reflexive, although "happens-before" would intuitively correspond to an irreflexive order. Since an event is never write and read action at the same time, this detail does not affect the semantics.

A:6 Andreas Lochbihler

Fig. 2: Happens-before provides a notion of time relative to a given event  $\alpha$ . If  $\alpha$  is a *Read*, it may see *Write* events in the grey area.

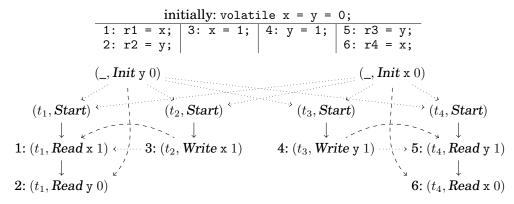

Fig. 3: Program from Fig. 1a in simpler syntax (a) and its JMM execution for the result r1 == r2 == 1 (b).

synchronises-with order  $\leq_{sw}$  captures these relationships between events of different threads, see §2.4 for the formal definition.

Whenever  $\alpha$ 's thread cannot deduce – using only allowed means of synchronisation – that an event  $\beta$  of another thread must have happened before or will happen after  $\alpha$ , then  $\alpha$  and  $\beta$  may happen concurrently. In particular, the thread must not make any assumption about the relative order of two events that happen concurrently. This permits compilers and hardware to freely reorder independent statements of a thread without synchronisation in between.

Finally, the synchronisation order  $\leq_{so}$  totally orders all synchronisation events and must be consistent with happens-before. It models a global time on synchronisation events on which all threads must agree.

Since the JMM is independent from a concrete language and sequential semantics, it is custom to write examples such as in Fig. 1a in a simple imperative language (Fig. 3a) rather than to obfuscate the point by irrelevant Java details. In this language, thread-local variables start with "r", e.g., r1, r2, whereas x, y, etc. denote shared locations. In examples, vertical rules separate the threads, and the thread in column i has ID  $t_i$ . Above the threads, the initial values of shared locations and any necessary declarations are given.

Fig. 3b shows how executions are depicted. The threads are abstracted to events – labelled with the thread ID – and orders. Solid arrows — represent program order, transitive relationships are not shown. The dashed arrows — denote the flow of values from writes to reads; the *write-seen function* of an execution assigns to each read event the write event it sees. Dotted arrows — used in later examples denote synchronisation (synchronises-with relationships).

The JMM requires that the write-seen function respects happens-before in the following sense: A read  $\alpha$  may see a write  $\beta$  that happens before or may happen concurrently (grey area in Fig. 2), but the write must not happen after the read. Moreover, there must not be another write  $\gamma$  to that location that is known to happen between  $\alpha$  and  $\beta$ , i.e.,  $\beta \leq_{\mathrm{hb}} \gamma \leq_{\mathrm{hb}} \alpha$ .

The execution shown in Fig. 3b results in r1 == r2 == 1, which SC does not allow. As there is no synchronisation, happens-before coincides with program order. Hence, ll. 1 and 2 may happen concurrently with ll. 3 and 4. Therefore, l. 1 and l. 3 are allowed to see the writes from l. 4 and l. 2, respectively. In particular, the thread on the left

Fig. 4: The classic independent reads of independent writes (IRIW) example

must not deduce that l. 3 must have already executed from the fact that l. 1 reads the value 1 from l. 4, because there is no synchronisation involved.

These constraints alone, which happens-before imposes on the visibility of writes, are insufficient to enforce global time. Figure 4 shows the classic independent reads of independent writes (IRIW) example [Boehm and Adve 2008]. In the execution depicted,  $t_1$  perceives l. 3 to execute before l. 4, because its reads see the former write, but y's initialisation instead of the latter write. Conversely,  $t_4$ 's reads see l. 4 and x's initialisation, but not l. 3. Hence, it appears to  $t_4$  as if l. 3 executes after l. 4. Such a result is possible if, e.g.,  $t_2$  and  $t_3$  execute simultaneously on different cores such that  $t_2$ 's core propagates the write to  $t_1$ 's core faster than to  $t_4$ 's and conversely  $t_3$ 's core communicates faster with  $t_4$ 's than with  $t_1$ 's (e.g., because they share their caches). However, no SC execution can produce such a result. By the DRF guarantee, the JMM must not allow this result either, because there are no data races (all shared locations x and y are marked as volatile). This is why volatile reads must also respect the synchronisation order analogously to happens-before. In Fig. 4, there is no such synchronisation order, because either l. 3 or l. 4 would be an intervening write between the initialisation of x or y and the read in l. 2 or l. 6, respectively.

1.1.3. Values Out of Thin Air. The constraints from happens-before and synchronisation order capture the JMM notion of a well-formed execution. However, they are still too weak for programs with data races. Consider, e.g., the program in Fig. 5a. In this program, the threads merely copy x to y and vice versa; the thread-local assignment in l. 3 has no effect and could well be removed. So one would expect r1 = r2 = 0 to be the only possible result. However, a queer compiler might eliminate the local variable r2 in the thread on the right: x = 1; x = y; is a correct implementation in a sequential setting, but in parallel with the thread on the left, the result r1 = 1 becomes possible even under interleaving semantics (e.g., schedule x = 1; r1 = x; y = r1; x = y;). As the original program cannot normally produce 1, 1 appears out of thin air. Yet, the constraints mentioned so far do not forbid this behaviour even for the original program. The reads in ll. 1 and 3 may see the writes in ll. 4 and 2, respectively, as they may happen concurrently and there is no synchronisation at all. Thus, Fig. 5b shows a well-formed execution for Fig. 5a.

For type safety and Java's security guarantees, it is vital that values do not appear out of thin air [Pugh 2000]. Otherwise, malicious code could exploit this to forge a pointer to an object to which it must not gain access or which it can then access in a type-unsafe fashion. For example, if 1.3 in Fig. 5a stored in r2 such a pointer instead

A:8 Andreas Lochbihler

initially:

$$x = y = 0$$

;

1:  $r1 = x$ ; | 3:  $r2 = 1$ ;

2:  $y = r1$ ; | 4:  $r2 = y$ ;

5:  $x = r2$ ;

(a)

1:  $(t_1, Read \times 1)$  | 4:  $(t_2, Read \times 1)$  | 4:  $(t_2, Read \times 1)$  | 4:  $(t_2, Read \times 1)$  | 5:  $(t_2, Write \times 1)$

Fig. 5: JMM causality test case 4 with 1.3 added: the value 1 appears out of thin air

of the value 1, such optimisations would enable the thread on the left to gain access to the pointer. Therefore, the JMM must forbid values appearing out of thin air. But note that the executions in Figs. 3b and 5b are identical when viewed in isolation. Yet, the JMM only allows the former. Thus, one cannot decide whether an execution is allowed by looking solely at the execution. In fact, being allowed is a second-order property.

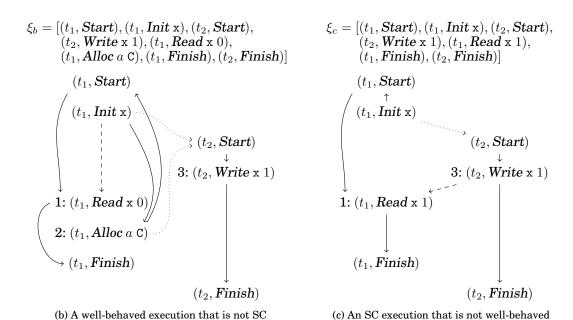

To ban self-justifying speculations (and distinguish Fig. 3b from Fig. 5b), the JMM adds a causality condition called *legality*: Reads that see concurrent writes must be committed, i.e., there must be a justifying JMM execution that produces the same value, but the read event  $\alpha$  sees a write event  $\beta$  that happens before it ( $\beta \leq_{\rm hb} \alpha$ ). This causality condition distinguishes the JMM from memory models of other languages like C++, where concurrent reads and writes immediately result in undefined behaviour. For Fig. 5a, causality forbids r1 == r2 == 1, because no execution can produce the value 1 without having both reads see the concurrent writes. In contrast, it accepts Fig. 3b, because Fig. 3a has another execution in which ll. 2 and 4 write 1 even if ll. 1 and 3 see the initialisations. The important thing to note is that at the basis of any sequence of justifying executions, there is one in which all reads see writes that happen before them. Such an execution is called *well-behaved*.

This is where memory initialisations come into play; the JMM assumes that all locations are initialised to their default value. To ensure that such a basis for justifying executions always exists, these initialisation events are defined to happen before any other event, i.e., conceptually at the start of the execution. Thus, there is always at least one suitable write that happens before any given read.

The details of the causality condition are the most complex part of the JMM. In fact, there are two versions: Aspinall and Ševčík [2007a] weakened the original condition such that more optimisations are possible while maintaining the DRF guarantee. I have formalised both and the theorems hold for both.

### 1.2. A Note on Coinduction

My formalisation heavily uses coinductive definitions and proofs. They provide an elegant way to handle finite and infinite executions uniformly. To make the formalisation and proofs more accessible, I now introduce the coinductive concepts that are used and compare them to their inductive counterparts, using a simple example. Readers familiar with coinduction may skip this section.

1.2.1. Coinductive Definitions. Like an inductive definition, a coinductive definition is given by inference rules; I use double horizontal bars to distinguish them from inductive ones. Formally, the rules are interpreted as a fixed point of the associated (monotone) functional  $\mathcal{F}$ : the least for inductive ones and the greatest fixed point (gfp) for coinductive ones.

The least fixed point (lfp) yields the *smallest* set that is closed under the rules. Hence, for each element, there is a finite derivation tree using only the introduction rules. In this sense, inductive definitions contain only finite elements. Therefore, one can use

induction to prove that all elements satisfy a property – abstractly, the inductive proof shows that the property is closed under the rules, too.

For example, given a labelled transition system (LTS), the following defines the family  $(\Pi_s)_s$  of sets of all maximal paths that start in a given state s.

$$P_1 \colon \frac{s \not\to}{\prod \in \Pi_s} \qquad \qquad P_2 \colon \frac{s \xrightarrow{l} s' \qquad \pi \in \Pi_{s'}}{l \cdot \pi \in \Pi_s}$$

Here,  $s \stackrel{l}{\rightarrow} s'$  denotes that state s can transition to s' with label l. A path is modelled as a word of labels; it is maximal iff it is infinite or it leads to a state s from which no transition is possible (notation  $s \not\rightarrow$ ). This example simplifies the actual construction I use for connecting Java with the JMM (§2.3): the LTS corresponds to the interleaved small-step semantics and the paths to traces of an execution. The monotone functional  $\mathcal F$  associated with  $P_1$  and  $P_2$  transforms a family  $A = (A_s)_s$  of sets to the family  $(\mathcal F(A)_s)_s$  as follows:

$$\mathcal{F}(A)_s = \begin{cases} \{ \ [ \ ] \ \} & \text{if } s \not\to \\ \{ \ l \cdot \ \pi. \ \exists s'. \ s \xrightarrow{l} s' \land \pi \in A_{s'} \ \} & \text{otherwise} \end{cases}$$

When  $P_1$  and  $P_2$  are interpreted inductively,  $\Pi_s = \mathit{lfp} \, \mathcal{F}$  consists of all *finite* maximal paths that start in s. The paths are finite, because each rule application (i.e., every step in  $\mathcal{F}$ 's fixed point iteration) adds just one label to the path. Hence, the inductive interpretation covers only finite, terminating executions.

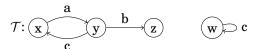

For the following transition system  $\mathcal{T}$ , e.g.,  $\Pi_x$  consists of the paths  $(ac)^n$ ab where n is any natural number. Here, I have omitted the cons operator  $\cdot$  and list brackets;  $\pi^n$  denotes n repetitions of  $\pi$  and  $\pi^\infty$  infinitely many. Inductively, one however obtains  $\Pi_w = \emptyset$ , because the only maximal path  $c^\infty$  from w is infinite.

In contrast, the greatest fixed point  $gfp \mathcal{F}$ , i.e., the coinductive interpretation, denotes the *greatest* set all of whose elements are justified by one of the inference rules – Pierce [2002] calls such sets consistent. It excludes only elements for which one can prove (in a finite derivation) that they do not belong to the set. Of course, the gfp contains all the finite elements with finite derivation trees. In addition, it typically includes infinite elements backed by infinite derivation trees. Hence, there is no rule for (structural) induction.

1.2.2. Coinduction and Infinite Derivation Trees. To show membership of an infinite element x, one uses coinduction: find a set A with  $x \in A$  such that A is consistent, i.e., all of A's elements are justified by one of the rules (formally  $A \subseteq \mathcal{F}(A)$ ). This proof principle is derived from greatestness: the gfp is the greatest consistent set and therefore a superset of A; in particular, it contains x. For example,  $\mathbf{c}^{\infty} \in \Pi_{\mathbf{w}}$  under the coinductive interpretation of  $\mathbf{P}_1$  and  $\mathbf{P}_2$ : Choose  $A_{\mathbf{w}} = \{\mathbf{c}^{\infty}\}$  and  $A_s = \emptyset$  for  $s \neq \mathbf{w}$ . I must show that whenever  $\pi \in A_s$ , either  $s \not\to$  and  $\pi = []$ , or  $\pi$  has the form  $l \cdot \pi'$  such that  $s \xrightarrow{l} s'$  and  $\pi' \in A_{s'}$  for some s'. The latter clearly holds for the chosen  $(A_s)_s$ :  $\mathbf{c}^{\infty} = \mathbf{c} \cdot \mathbf{c}^{\infty}$  and  $\mathbf{w} \xrightarrow{c} \mathbf{w}$ . Similarly,  $\Pi_{\mathbf{x}}$  contains also  $(\mathbf{ac})^{\infty}$  under the coinductive interpretation (provable with a different choice for  $(A_s)_s$ ).

Note that (in)finiteness describes the derivation trees, not the elements themselves. In the example, both rules add one constructor. So, a path is finite iff it has a finite

derivation. But this does not hold in general. Suppose, e.g., that the label c signifies an internal computation that should not show up in a trace. The following attempt defines the family  $(\Pi_s')_s$  of sets of all maximal paths from s from in which the label c has been purged. It splits the rule  $P_2$  into  $P_2'$  and  $P_D'$ . If the next transition has label c,  $P_D'$  does not cons the label. This breaks the correspondence between constructors and derivation steps.

$$P_1'\colon \frac{s\not\to}{\|\in\Pi_s'} \qquad P_2'\colon \frac{s\stackrel{l}{\to}s' \quad \pi\in\Pi_{s'}' \quad l\neq \mathbf{c}}{l\cdot\pi\in\Pi_s'} \qquad P_{\mathtt{D}}'\colon \frac{s\stackrel{\mathbf{c}}{\to}s' \quad \pi\in\Pi_{s'}'}{\pi\in\Pi_s'}$$

Now,  $[] \in \Pi'_w$  is a path of finite length, but its (only) derivation is infinite, namely infinitely many applications of  $P'_D$ . Formally, this is again shown by coinduction: choose  $A_w = \{[]\}$  and  $A_s = \emptyset$  for  $s \neq w$ ; justify  $[] \in A_w$  with  $P'_D$ :  $w \xrightarrow{c} w$  and  $[] \in A_w$ . Computationally, it is sensible to consider [] as infinite, because it models a non-terminating computation with only internal steps.

For both  $c^{\infty} \in \Pi_w$  and  $[] \in \Pi'_w$ , the justifying element in  $A_{s'}$  was  $c^{\infty}$  and [], respectively. That is, they justified themselves. For  $(\Pi_s)_s$ , self-justification is unproblematic, because all rules add constructors. Hence, the infinite derivation traverses all of  $c^{\infty}$  – it is a mere coincidence that  $c^{\infty}$  is equal to its tail. For  $[] \in \Pi'_w$ , this argument fails, because  $P'_D$  applies infinitely often without changing the path, i.e., the infinite derivation completely ignores the structure of []. In fact,  $\Pi_w$  contains junk: coinduction similarly shows that any path  $\pi$  is a member of  $\Pi'_w$ , not just  $\pi = []$ . Thus,  $P'_1$ ,  $P'_2$ , and  $P'_D$  are wrong (although they would be fine for an inductive definition).

In fact, it is hard to characterise  $(\Pi'_s)_s$  coinductively, but there is an elegant way out: Define  $\Pi'_s = \{ purge \ \pi. \ \pi \in \Pi_s \}$  where the function purge (defined corecursively below) removes all occurrences of c from a list. Single-valuedness ensures that no junk is introduced. Hence,  $\Pi'_w = \{ [] \}$  as desired. In §2.3, I use a similar approach to remove unobservable transitions in traces. (To indicate that a variable is a list, I often draw a bar across the variable like in  $\overline{x}$ ; list variables  $\overline{x}$  are distinct from those without bars, e.g., x, which usually denote an element of such a list.)

$$\begin{array}{ll} \textit{purge} & \overline{x} & = \textit{purge'} \; (\textit{dropWhile} \; (\lambda y. \; y = \mathbf{c}) \; \overline{x}) \\ \textit{purge'} & [] & = [] \\ \textit{purge'} \; (x \cdot \overline{x}) = x \cdot \textit{purge'} \; (\textit{dropWhile} \; (\lambda y. \; y = \mathbf{c}) \; \overline{x}) \end{array}$$

As this definition steps out of the language of coinduction, coinduction as proof principle no longer works out of the box. For example,  $no\text{-}c\ \overline{x}$  defined by  $NC_1$  and  $NC_2$  formalises that the list  $\overline{x}$  does not contain c. Let me show that all paths in  $\Pi_s'$  in fact do not contain c, i.e., that  $no\text{-}c\ (purge\ \pi)$  holds for any  $\pi\in\Pi_s.^6$

$$ext{NC}_1 : \frac{ ext{no-} c \ \overline{x} ext{} ext{} x

eq c}{ ext{no-} c \ (x \cdot \overline{x})}$$

I must use coinduction, as  $\pi$  and  $purge\ \pi$  may be infinite, i.e., induction is not available. Note that in the coinductive step, every justification with NC<sub>2</sub> must produce one label of the (purged) path. However, dropWhile in purge's definition may gobble arbitrarily many labels of  $\pi$ . Hence, such a justification requires unbounded search for the state that produces the next label other than c in  $\pi$ .

<sup>&</sup>lt;sup>6</sup>Actually, no-c (purge  $\overline{x}$ ) holds for any list  $\overline{x}$ , not just paths  $\pi \in \Pi_s$ . Nevertheless, to illustrate the idea of termination parameters, I thread the premise  $\pi \in \Pi_s$  through the coinductive proof.

1.2.3. Termination Parameters. To avoid complicated proofs, I introduce a termination parameter a which is taken from a well-founded order  $(R, \prec)$ . This way, I can delay the justification in the coinductive step provided that a decreases in  $\prec$ . The parametrised  $no\text{-}c_a$  adds to no-c's rules the delay rule  $NC'_D$ . Its premise  $a' \prec a$  and well-foundedness ensure that any derivation tree applies the rule  $NC'_D$  only finitely many times in a row – this avoids the junk due to self-justifications. As the other recursive rule  $NC'_2$  adds a constructor, the termination parameter may be chosen anew after each application.

$$NC_{1}' : \frac{\mathbf{no-c}_{a'} \ \overline{x} \qquad x \neq \mathbf{c}}{\mathbf{no-c}_{a} \ []} \qquad NC_{2}' : \frac{\mathbf{no-c}_{a'} \ \overline{x} \qquad x \neq \mathbf{c}}{\mathbf{no-c}_{a} \ (x \cdot \overline{x})} \qquad NC_{D}' : \frac{\mathbf{no-c}_{a'} \ \overline{x} \qquad a' \prec a}{\mathbf{no-c}_{a} \ \overline{x}}$$

Then,  $\operatorname{no-c} \overline{x}$  iff  $\operatorname{no-c_a} \overline{x}$  for some  $a \in R$ . Thus, I can use  $\operatorname{no-c_a}$ 's coinduction principle to prove that  $\pi \in \Pi'_s$  does not contain c. For  $\prec$ , I take as measure the length of  $\pi$ 's prefix of c labels. Hence, when the first label in  $\pi$  is c (and I normally would have to start an unbounded search to gobble all c labels), I merely drop the first label and I use  $\operatorname{NC}'_D$  for justification, as the measure decreases.

Formally, Isabelle/HOL represents the coinduction principle as an ordinary higherorder theorem. Hence, I do not need to define  $no\text{-}c_a$  explicitly and prove equivalence to no-c. It suffices to prove the new coinduction principle with delay as a theorem like it would be generated for  $no\text{-}c_a$ . This proof is a trivial induction on well-foundedness and can be easily automated. In this work, I use delayed coinduction when building sequentially consistent completions (Lem. 3.20) and well-behaved executions.

### 2. LINKING JAVA WITH THE JAVA MEMORY MODEL

This section describes how to formally connect Java and Java bytecode with the Java memory model. I build on the JinjaThreads model of Java and Java bytecode, which I have described in detail in previous work [Lochbihler 2007; 2008; 2010; 2012b; Lochbihler and Bulwahn 2011]. It covers a substantial subset of sequential Java and Java bytecode, e.g., local variables and assignments, objects and fields, inheritance, dynamic dispatch, recursion, arrays, exception handling, standard control structures, and native methods. It models the following multithreading features according to the Java language specification (JLS) [Gosling et al. 2005]: arbitrary thread creation, synchronisation through monitors, the wait-notify mechanism, joining on threads, thread interruption, and volatile fields. JinjaThreads is executable [Lochbihler and Bulwahn 2011] and has been validated by running Java test programs [Lochbihler 2012b].

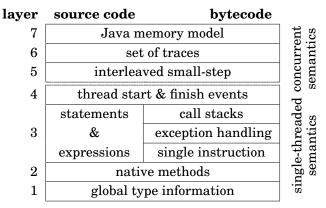

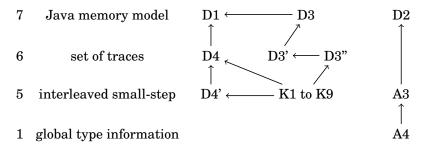

To favor reuse and sharing, I have organised the semantics in a stack (Fig. 6). It falls into two parts: Layers 1 to 4 define the single-threaded semantics and layers 5 to 7 the multithreaded ones. This separation nicely disentangles all intra-thread issues from concurrency; both parts only communicate using events à la JMM inter-thread actions. Similarly, each layer connects to the layer above through an interface of signatures and assumptions, on which the definitions and proofs rely. Moreover, this structure favors reuse between the source code and bytecode: their formalisations differ only in layer 3, which defines the semantics of the language primitives.

The presentation omits some uninteresting details of the semantics. Instead, I focus on the following challenges:

<sup>&</sup>lt;sup>7</sup>These termination parameters are orthogonal to up-to techniques that are common in bisimulation proofs [Sangiorgi 1998; Hur et al. 2013]. Up-to techniques allow to pick the justification of elements in the coinduction invariant from a larger set, but still require that the elements are immediately justified according to one of the rules. In contrast, my parametrisation over a well-founded order allows to defer *before* committing to one rule. In the following *no-c* example, up-to techniques do not help to prove c being absent in paths taken from  $\Pi'_s$ , because *dropWhile* delays the decision between NC<sub>1</sub> and NC<sub>2</sub> for arbitrarily many steps. Without parametrisation, the coinduction proof requires a nested induction.

Fig. 6: JinjaThreads stack of semantics

- storing runtime type information and allocating fresh memory (§2.1, §2.6, §2.7),

- deriving event traces from the single-threaded semantics (§2.2, §2.3),

- formalising the JMM (§2.4)

- determining the identity of an event (§2.5),

- dealing with non-termination (§2.8), and

- modelling the wait-notify mechanism and interruption (§2.9, §2.10).

## 2.1. Type Information and Fresh Addresses

In the informal introduction §1.1, I have only mentioned values in heap locations. Yet, a Java implementation must also exchange runtime type information, array lengths, and freshness of addresses between the threads. According to the JLS [Gosling et al. 2005, §17.4.5], checked type casts, virtual method calls, and reading the length of an array are not part of the inter-thread actions and thus not affected by the JMM; reading types and array lengths must always return the correct data. Therefore, the JMM provides the strong model of sequential consistency for type information, and array lengths.

To enforce SC for types, I implement allocation and type information as a global state. The multithreaded semantics passes this global state from one thread to the other during execution like in interleaving semantics. Moreover, I define abstract operations to query and update the global state and specify their properties. Hence, I am able to state clearly what assumptions type safety and the DRF guarantee rely on. Along the way, this addresses a question pointed out by Aspinall and Ševčík [2007a]: What does it mean for an address being fresh for memory allocation?

The interface to the shared state consists of three operations:

- (1) The partial function *typeof-addr*  $\sigma$  *a* extracts from the state  $\sigma$  the type information for address *a*, i.e., the type of the object at *a* and possibly its array length.

- (2)  $empty-\sigma$  denotes the initial state when no objects have been allocated.

- (3) The non-deterministic function alloc  $\sigma$  T allocates a new object or array of type  $T^9$  and returns its fresh address and the updated state. To model non-determinism, alloc returns a set of pairs of addresses and state such that the higher levels can

<sup>&</sup>lt;sup>8</sup>Although the JLS specifies that every array has a final field length [Gosling et al. 2005, §6.4.5] that stores its length, the JMM treats array lengths specially [Gosling et al. 2005, §17.4.5].

<sup>&</sup>lt;sup>9</sup>I assume that the type of an array also specifies its length.

```

class A { void m() {} } initially: x = y = null;

1: r1 = x;

2: if (r1 != null) r1.m();

3: r3 = new A();

4: y = r3;

```

Fig. 7: Dynamic dispatch in l. 2 requires type information which is not yet available

propagate the non-determinism – I discuss the need for non-determinism in §2.6. If all addresses are already allocated, the set is empty.

The implementation must ensure two properties:

- (A1) alloc is correct, i.e., if  $(\sigma', a) \in alloc \ \sigma \ T$ , then  $\sigma'$  stores type T for a, i.e.,  $typeof-addr \ \sigma' \ a = \lfloor T \rfloor$  (where  $\lfloor \_ \rfloor$  denotes definedness).

- (A2) alloc only extends the type information in  $\sigma$ , i.e., if typeof-addr  $\sigma$   $a = \lfloor T \rfloor$  and  $(\sigma', a') \in$ alloc  $\sigma$  T', then typeof-addr  $\sigma'$  a = |T|.

In the following, I implement this specification twice (§2.1.1 and §2.1.2).

2.1.1. Dynamic Type Information. The first implementation stores the type of objects in the objects themselves. This follows standard practice in formalising Java [Alves-Foss 1999; Stärk et al. 2001; Liu and Moore 2003; Klein and Nipkow 2006; Farzan et al. 2004b; Petri and Huisman 2008]. The global type information  $\sigma$  is like a shared heap (a map) except that it stores for every allocated address instead of the object itself only its type and possibly the array length, but no field values. Field values are irrelevant, because the JMM determines them. I implement the operations as follows: typeof-addr  $\sigma$  a merely returns the information that  $\sigma$  stores for a; empty- $\sigma$  is the everywhere undefined map; and alloc  $\sigma$  T returns the set of all addresses fresh in  $\sigma$  and pairs each such address a with  $\sigma$  updated to store T for a. An address is fresh in state  $\sigma$  iff  $\sigma$  contains no type information for it. This implementation is straightforward and satisfies the above specification (A1 and A2).

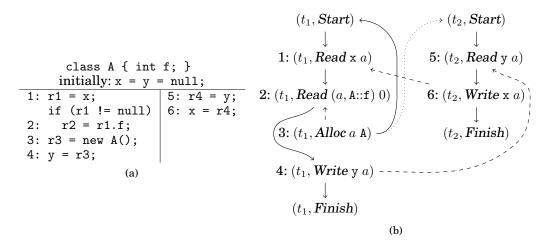

However, programs with data races may have type-unsafe executions. In the following two examples, the program gets stuck or subject reduction fails. They both exploit that the type of an address is only determined upon allocation, but not when it is first used. Nevertheless, the DRF guarantee applies (§3) and ensures that programs without data races are type safe like under SC.

First, when the type of an address is not yet known, the defensive (source code) semantics can get stuck and the aggressive virtual machine (VM) behaves in an undefined way. The example in Fig. 7 has data races on x and y. The JMM allows that 1.1 reads the address a of the object allocated in 1.3 via the detour of the second thread, because an optimising compiler might move 1.3 and 4 before 1.3. However, the semantics does not anticipate such optimisations, but executes the program as it is. Hence, when 1.3 calls m on a, the defensive source code semantics gets stuck and the aggressive VM calls an unspecified method, because a's type information used for dynamic dispatch is still undefined.

A temptingly simple measure would be to restrict reading such that only allocated addresses may be read from memory. However, the semantics then misses some legal JMM behaviours, because this restriction prohibits reordering with memory allocations. In Fig. 7, e.g., the JMM allows r1 == y in the final state, because compilers are allowed to move l. 1 past the independent statements in ll. 3 and 4. However, the restricted semantics cannot produce this result because the read in l. 1 always executes before the allocation in l. 3, i.e., it can never return the address to be allocated.

A:14 Andreas Lochbihler

Fig. 8: A program with a legal execution where r2 of type D references a C object

Second, reading an address before its type is determined may also compromise subject reduction. The program in Fig. 8 is type correct if it declares x, y and r2 of type D. However, it has a legal execution where they reference a C object (for a detailled derivation, see Fig. 27). The problem here is that the type of an address may vary across justifying executions. The allocation operation *alloc* may pick the *same* address a for the allocations in ll. 5 and 7, because only one of them occurs in any one execution. Hence, it is l. 4 that decides on the type to allocate — based on whether it sees the initialisation b = false or the concurrent write b = true. However, l. 3 may have already read a and stored it in r2 of static type D. Then, if l. 5 allocates a C object, type safety is broken.

2.1.2. Static Types for Addresses. To tackle the above type safety issues, I define the following alternative implementation of the operations. It is motivated by the insight that the core of the above problems is that the type of an address is only determined upon allocation, but not when it is first used.

Now, it is the address itself that stores type information for the address. Hence, an address a=(T,n) consists of its type information T and a sequence number n to distinguish objects of the same type. The type and array length of an address is the information stored in the address, i.e., typeof-addr  $\sigma$   $(T,n)=\lfloor T \rfloor$ . In particular, type information for every address is available from the start. Hence, the programs in Figs. 7 and 8 are unproblematic, because with this implementation,

- (1) dynamic dispatch only requires correct type information, which is now available independent of allocations, and

- (2) the allocations in ll. 5 and 7 always return different addresses.

Now that I have stripped type information off the shared state, it only needs to remember which addresses are fresh for allocation. Hence, the state maps type information to the set of sequence numbers of objects of that type that have already been allocated. To allocate an object of type T in state  $\sigma$ , allocation produces a pair  $(\sigma', (T, n))$  for every sequence number  $n \notin \sigma T$  where  $\sigma'$  updates  $\sigma$  to store  $\sigma T - \{n\}$  at T. Obviously, this implementation satisfies the specification A1 and A2, too.

Apart from supporting type safety, this implementation exposes a hidden communication channel via type information from which the previous suffered. For example,

```

class A implements I { int f() { return 0; } }

class B implements I { int f() { return 1; } }

interface I { int f(); } initially: x = 0; y = null;

1: r1 = x;

2: r2 = (r1 == 0 ? new A() : new B());

3: y = r2;

(P1)

```

Classes A and B inherit method f() from their common interface I. When 1.5 sees 1.3, dynamic dispatch at 1.6 tells the thread on the right about the left thread's local variable r1, although there is no synchronisation involved. In the previous implementation, the allocation in 1.2 returns the same address value, no matter whether A or B is allocated. Hence, from the point of view of events, the thread on the right only reads an address (in fact the same value in both cases), but behaves differently. In contrast, the second implementation allocates A's objects at different addresses than B's. Hence, the value that 1.5 reads completely determines the call target in 1.6. Analogously, threads can communicate through array lengths instead of types, see Fig. 25 for an example. This is why I treat array lengths as part of the type information – arrays of different lengths have distinct addresses.

However, there is also a disadvantage over the previous implementation. Since type information partitions the address space, each read or write of an address value not only transfers a pointer value as on standard hardware, but simultaneously does so for the complete run-time type information of the object it references. From an implementation point of view, this is unrealistic.

## 2.2. Thread Management Actions

As the global state needs to be passed between the threads, threads cannot execute in isolation, as the JMM suggests [Gosling et al. 2005, §17.4]. Instead, I compute their interleavings, which guarantees sequential consistency for the shared type information. My interleaving semantics also takes care of mutual exclusion for locks and manages the monitor wait sets, notifications, spawns of and joining on threads, and thread interruption.

The single-threaded semantics has the form  $t \vdash (x, \sigma) - \overline{\alpha} \rightarrow (x', \sigma')$ . Local states of thread t are denoted by x and x', and  $\sigma$ ,  $\sigma'$  are the (global) type information that all threads share. Source code defines a small-step semantics, the VM for bytecode uses a functional style. Both semantics are standard except for three aspects:

- (1) They can access only the local state of the current thread and the shared state of type information, but not, e.g., the thread pool, the wait sets, or other thread's local states. Instead, they use a list  $\overline{\alpha}$  of events to communicate with the interleaving semantics. This separates the concurrency features from the sequential aspects such that I can use the same interleaving semantics for Java source code and bytecode. Figure 9 shows the source code reduction rules for calls to *Thread*'s native methods *start*, *interrupt*, and *isInterrupted*. As can be seen, these rules merely translate the method calls to appropriate events for the multithreaded semantics. I will discuss the specific events below.

- (2) As there is no shared state that stores the values of object fields and array cells, the thread does not know what value should be read. Non-determinism solves this. When a thread needs to read a field or array cell, there is a separate transition for every value that could be read, even for type-incorrect ones. Although this produces many impossible reductions, the JMM well-formedness and legality constraints will later select the right ones. To that end, read and write operations are recorded in the list  $\overline{\alpha}$ , too. For example, the rules for reading and writing field  $C:F^{10}$  of the object at address a are as follows. Note that the shared state  $\sigma$  does not constrain value v at all.

$$\begin{split} & \textbf{FAcc:} & t \vdash (\textit{addr}\ a.C.:F,\sigma) - [\textit{Read}\ (a,C::F)\ v] \rightarrow (\textit{Val}\ v,\sigma) \\ & \textbf{FAss:} & t \vdash (\textit{addr}\ a.C.:F := \textit{Val}\ v,\sigma) - [\textit{Write}\ (a,C::F)\ v] \rightarrow (\textit{unit},\sigma) \end{split}$$

$<sup>\</sup>overline{\ }^{10}$ To distinguish hidden fields, a field is labelled with the class that declares it, e.g., C::F denotes F declared in C.

A:16 Andreas Lochbihler

```

\begin{split} \text{SP:} & \quad t \vdash (addr\ a.start([]),\sigma) - [Spawn\ a\ (C,run,a)] \rightarrow (unit,\sigma) \\ \text{SPF:} & \quad t \vdash (addr\ a.start([]),\sigma) - [ThreadEx\ a\ True] \rightarrow (throw\ IllegalThreadState,\sigma) \\ \text{INTR:} & \quad t \vdash (addr\ a.interrupt([]),\sigma) - [ThreadEx\ a\ True,\ WakeUp\ a,\ Intr\ a] \rightarrow (unit,\sigma) \\ \text{INTRINEX:} & \quad t \vdash (addr\ a.interrupt([]),\sigma) - [ThreadEx\ a\ False] \rightarrow (unit,\sigma) \\ \text{ISINTRDT:} & \quad t \vdash (addr\ a.isInterrupted([]),\sigma) - [Intrd\ a] \rightarrow (true,\sigma) \\ \text{ISINTRDF:} & \quad t \vdash (addr\ a.isInterrupted([]),\sigma) - [NotIntrd\ a] \rightarrow (false,\sigma) \\ \end{split}

```

Fig. 9: Semantics of methods start and isInterrupted for class Thread. All rules have the preconditions typeof-addr  $\sigma$   $a = \lfloor T \rfloor$  and that T inherits the called method from class Thread.

(3) The semantics ensure that the first transition of every thread generates the *Start* event and – if the thread terminates – the last transition the *Finish* event. Layer 4 in the stack of semantics takes care of this.

Just like the single-threaded semantics does not know anything about the other threads, the multithreaded semantics is oblivious of the thread-local states and the shared type information. The multithreaded state stores the state of all locks, the wait sets and notifications, the pending interrupts and the threads' local states.

When the interleaving semantics interleaves the reductions of the individual threads (notation  $s-(t,\overline{\alpha})\to s'$ ), it checks that the events  $\overline{\alpha}$  of t's reduction are in line with the current multithreaded state s. For example, if  $\overline{\alpha}$  contains a Lock a event, then the lock a must not currently be held by any thread other than t. And in case of a Spawn a event, the thread identified by object a must not have been spawned yet. Implementing all this is tedious – see [Lochbihler 2012b, Ch. 3] for the definitions –, but the full details are not relevant for the rest of this paper. I write  $s-\overline{ta}\to s'$  for the reflexive and transitive closure of  $s-s\to s$ , where  $s\to s$  is a list of pairs  $s\to s$  of thread ID and event list  $s\to s$ .

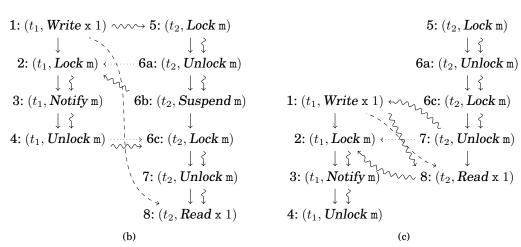

Unfortunately, the events from §1.1 are insufficient to correctly implement the JLS. Therefore, I introduce the following additional events:

- (1) Detect whether a thread has already been spawned (*ThreadEx*),

- (2) wait in a monitor (Suspend) and notification (Notify, NotifyAll, WakeUp),

- (3) clearing an interrupt (*ClearIntr*) and testing for a thread not being interrupted (*NotIntrd*), and

- (4) test whether the current thread does (not) hold a lock (HasLock, NoLock).

Technically, the last group is only a convenience, because this way, a thread need not remember in its local state which locks it is holding. The others, however, are necessary as the examples P2, P3, P4, P5, and Fig. 20 will show.

For ThreadEx, consider program P2 of two threads that race for spawning the same thread:

Suppose both reads in ll. 3 and 5 see the write at l. 2, i.e., they read the address of the allocated *Thread* object. Then, either l. 4 or l. 6 must throw an *IllegalThreadState* exception, but not both. Hence, both l. 4 and l. 6 must be allowed to fail in some executions. Thus, the two right-most threads may just start, read the address of the

Thread object (then fail with the exception, but the JMM has no event for that), and then finish. Hence, if each thread were run in isolation, they both would be allowed to fail, too. Since this contradicts the specification of the *start* method, there is a covert communication channel.<sup>11</sup>

For the new interruption events, consider the following program.<sup>12</sup> Can we have r == 0 at the end?

Intra-thread consistency requires that 1.3 executes only after the loop in 1.2 has terminated. According to the API specification, isInterrupted() returns true as long as  $t_2$  is interrupted. As only 1.6 can clear the interrupt, 1.3 must execute after 11.5 and 11.5 and 11.5 must see the most recent write, i.e., consistency allows only 11.5 must be events 11.5 and 11.5 must see the most recent write, i.e., consistency allows only 11.5 must be events 11.5 must see the most recent write, i.e., consistency allows only 11.5 must be events 11.5 must see the most recent write, i.e., consistency allows only 11.5 must be events 11.5 must see the most recent write, i.e., consistency allows only 11.5 must be events 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must be events 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recent write, i.e., consistency allows only 11.5 must see the most recen

### 2.3. Traces

Given the interleaving semantics, the next step is to construct the execution candidates (called traces) from which the JMM rules will select the well-formed and legal ones. A trace  $\xi$  is a possibly infinite list of events labelled by the thread that generated them. The relation  $s \downarrow \xi$  characterises all traces  $\xi$  that start in the state s, which I define as

$$s \Downarrow \xi \longleftrightarrow (\exists \overline{\xi}. \ s \downarrow \overline{\xi} \land \xi = \mathbf{concat} \ \overline{\xi}) \tag{1}$$

where  $concat \bar{\xi}$  concatenates all lists in  $\bar{\xi}$  and  $s \downarrow \bar{\xi}$  (defined coinductively) collects the list of lists of events labelled with the thread ID as follows:

$$\frac{s \not \to}{s \downarrow \parallel} \text{ Stop} \qquad \frac{s - (t, \overline{\alpha}) \to s' \qquad s' \downarrow \overline{\xi}}{s \downarrow (events \ t \ \overline{\alpha}) \cdot \overline{\xi}} \text{ Step}$$

where  $\_ \not\rightarrow$  characterises stuck states in the interleaving semantics and events  $t \ \overline{\alpha}$  retains only the original JMM inter-thread actions (as defined in §1.1) from  $\overline{\alpha}$  and pairs each with the thread ID t. Hence, every trace is a complete list of the JMM events produced by running the program.

Note that the detour via a list of lists of events is necessary. If I defined  $s \Downarrow \xi$  directly with the above coinductive rules STOP and STEP (i.e., prepending events  $t \overline{\alpha}$  to  $\xi$  instead of consing), I could derive every trace  $\xi$  for a state s that can perform an infinite sequence of transitions without events, i.e., events  $t \overline{\alpha} = []$ , because it would be impossible to prove that  $\xi$  was not a trace (STEP would be applicable infinitely often as discussed in §1.2). The above approach works fine since (events  $t \overline{\alpha}$ )  $\cdot \overline{\xi}$  adds a constructor and concatenating the infinite list of empty lists yields the empty list [].

For the JMM, a program always comes with a fixed start state *start-state*. It is specified by a class, a method name, and the list of parameters it takes. It contains only a

$<sup>^{11}</sup>$ For start, the JMM specifies synchronisation only between a successful call and the first action of the spawned thread [Gosling et al. 2005, §17.4.4]. A JVM implementation might add more synchronisation, but our semantics must not, since this might eliminate data races from programs, i.e., it could wrongly certify programs with data races as DRF: for an example, see the program P8 and its data race between ll. 1 and 5 in §6.

$<sup>^{12}</sup>$ The method isInterrupted returns whether the receiver thread has been interrupted. The static method interrupted returns the interrupt status of the current thread and atomically clears the interrupt.

A:18 Andreas Lochbihler

```

class T0 {

public static void main(String[] args) {

C c = new C(); Thread t1 = new T1(c); Thread t2 = new T2(c);

t1.start(); t2.start(); }

class T1 extends Thread {

C c;

T1(C c) { this.c = c; }

public void run() { C c = this.c; int r1 = c.x; c.y = 1; } }

class T2 extends Thread {

C c;

T2(C c) { this.c = c; }

public void run() { C c = this.c; int r2 = c.y; c.x = 1; } }

class C { int x, y; }

```

Fig. 10: Java implementation for the example in Fig. 3

single thread *start-tID* that holds no locks and is about to execute the specified method with the given parameters. All wait sets are empty and there are no pending interrupts. The shared type information has pre-allocated the *start-tID* Thread object and certain system exceptions. The list *start-events* of start-up events contains *start-tID*'s *Start* event and allocations for the preallocated objects.

Then, the JMM identifies a program with the set  $\mathcal{E}$  of complete traces that start in *start-state*, prefixed with *start-events*. Formally (++ concatenates two lists):

```

\mathcal{E} = \{ start\text{-events} + + \xi \mid start\text{-state} \downarrow \xi \}

```

${\cal E}$  contains many ill-formed traces, because read operations may read arbitrary values, even not type-conforming ones that no write operation of the program can ever produce. Since such traces have no write-seen function, the JMM well-formedness rules discard them.

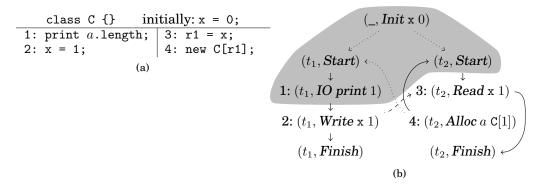

Let me now present an example of  $\mathcal{E}$  in detail. Fig. 10 shows a Java implementation of the example in Figs. 1 and 3. There is a bootstrapping thread  $t_0$  that creates and spawns the two threads  $t_1$  and  $t_2$  whose run methods contain the code from the example. Since JinjaThreads does not model static fields, the shared locations x and y are represented by the fields of a container class c.

All traces start with the following events that represent  $t_0$ 's main method up to the first call to *start*, abbreviated as *up-to-spawn*:

```

start-events ++ [(t_0, Alloc \ a_0 \ C), (t_0, Alloc \ t_1 \ T1), (t_0, Write \ (t_1, T1::c) \ a_0), (t_0, Alloc \ t_2 \ T2), (t_0, Write \ (t_2 \ T2::c) \ a_0), (t_0, Spawn \ t_1 \ \_))]

```

i.e.,  $t_0$  allocates the objects for the container and the two threads at locations  $a_0$ ,  $t_1$  and  $t_2^{13}$  and executes T1's and T2's constructors. Remember that the allocations initialise the fields with default values, i.e., 0 for x and y declared in C, and Null for c declared in T1 and T2.

Thread  $t_1$  has three structurally different traces depending on the kind of value that reading this.c stores in the local variable c, namely (the label  $t_1$  is omitted):

```

(1) [Start, Read (a_1, T1::c) (Addr a), Read (a, C::x) v, Write (a, C::y) (Intg 1), Finish],

```

$<sup>^{13}</sup>$ For simplicity, I assume in examples that threads are identified by the address of their associated object. If not mentioned otherwise, all examples abstract from the non-determinism in the allocator by using location names  $a_0$ ,  $t_1$ , and  $t_2$  instead of concrete addresses.

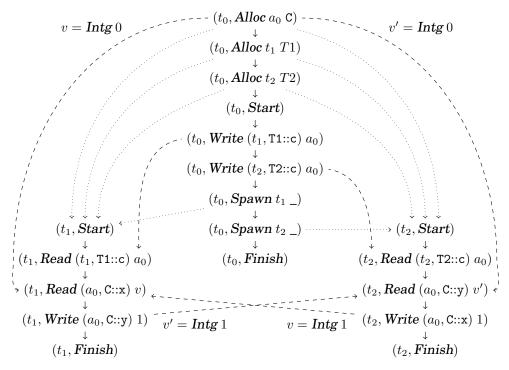

Fig. 11: Well-formed executions for the program in Fig. 10

- (2) [Start, Read ( $a_1$ , T1::c) Null, Finish], and

- (3) [Start, Read  $(a_1, T1::c) w$ ],

where a is an arbitrary address, v is an arbitrary value, and w is any value other than an address or the null pointer Null. In the first form, the address a from the Read is then used to access the fields x and y of the referenced container. In the second,  $t_1$  reads Null, so the subsequent field access raises the preallocated NullPointer exception and the thread immediately terminates. In the last case, w is type-incorrect, so the semantics gets stuck upon the next field access, i.e., there is no Finish. Thread  $t_2$  has the same traces with x and y exchanged.

The traces in  $\mathcal{E}$  for this program all start with up-to-spawn and then interleave the threads. Of these, the JMM considers only those as well-formed that originate from the first form with  $a=a_0$  and  $v,v'\in\{Intg\ 0,Intg\ 1\}$  (Intg injects 32 bit integers into the type of values). In particular, the unexpected behaviour from Fig. 3 is well-formed. In terms of the JMM, all these interleavings collapse to four well-formed executions as shown in Fig. 11 (where I have omitted the bootstrap events for clarity – except for  $t_0$ 's Start event that is relevant for determining what happens before what). The write-seen arrows are labelled with conditions for which they apply. All well-formed executions are legal in this example.

### 2.4. Formal Definition of the Java Memory Model

Now, I formalise the JMM and connect it with the set of traces  $\mathcal{E}$ . First, I introduce some JMM terminology (§2.4.1) and I derive the orders of the JMM from a trace (§2.4.2), which abstract from the concrete interleaving as explained in §2.3. Then, the

A:20 Andreas Lochbihler

formal definitions of well-formed and legal execution builds on these orders ( $\S 2.4.3$  and  $\S 2.4.4$ ).

2.4.1. JMM Terminology. Most JMM definitions depend on a trace  $\xi$ , which I usually attach as a sub- or superscript. To simplify the notation, I drop the sub- and superscript, when  $\xi$  is obvious from the context.

Since an event can occur multiple times in  $\xi$ , I use the index in  $\xi$  (a natural number) to assign a unique identifier to an event. Formally, an event identifier  $\alpha$  is just an index whose interpretation  $\xi_{[\alpha]}$  depends on the execution  $\xi$ . In the following, I usually blur this distinction: I use the variable  $\alpha$  for both indices and events, and – when it is clear from the context – I write  $\alpha$  instead of the interpretation  $\xi_{[\alpha]}$ . Hence,  $\mathcal{A}_{\xi} = \{ \alpha \mid \alpha < |\xi| \}$  denotes the set of events (more precisely, event identifiers) for  $\xi$ , where  $|\xi|$  denotes the length of  $\xi$ .

A read event is an event of the form  $(t, Read\ (a, l)\ v)$ , it reads from location (a, l) the value v;  $\mathcal{R}_{\xi}$  denotes the set of read events of  $\xi$ . A write event is either a write  $(t, Write\ (a, l)\ v)$  or an allocation  $(t, Alloc\ a\ T)$ ,  $\mathcal{W}_{\xi}$  denotes the set of write events in  $\xi$ . A write event  $\alpha \in \mathcal{W}_{\xi}$  writes to location (a, l) (is a write to (a, l)) iff  $\alpha = (\_, Write\ (a, l)\ \_)$ , or  $\alpha = (\_, Alloc\ a\ T)$  and l is a member of T (notation  $l \in memb\ T$ ). The members of a class C are all fields of C and its super-classes, and the members of an array type T[n] are the fields of Object and the array cells  $[0], \ldots, [n-1]$ . An allocation  $Alloc\ a\ T$  initialises all locations (a, l) for  $l \in memb\ T$ .

I say that  $\alpha$  accesses location (a,l) iff  $\alpha$  is a read or write event that reads from or writes to (a,l), respectively.  $locs\ \alpha$  denotes the set of locations that  $\alpha \in \mathcal{R} \cup \mathcal{W}$  accesses;  $locs\ \alpha = \emptyset$  for  $\alpha \in \mathcal{A} - (\mathcal{R} \cup \mathcal{W})$ .

For  $\alpha \in \mathcal{W}$ ,  $vw \alpha (a, l)$  denotes the value that  $\alpha$  writes to location (a, l) – allocation events  $(\_, Alloc \_T)$  write default values (0, False, and Null, respectively) for all members of T; normal writes Write (a, l) v store the value v written themselves;  $vw \alpha (a, l)$  is unspecified if  $\alpha$  does not write to (a, l).

A member l is volatile (written *is-volatile* l) iff l is a field C::F and class C declares F as volatile. A read or write  $\alpha$  is volatile iff  $\alpha$  reads from or writes to a volatile member of a location. In particular, array cells are never volatile by definition [Gosling et al. 2005, §8.3.1.4].

2.4.2. From Traces to Orders. A trace  $\xi$  already provides the induced total order  $\preceq^{\xi} = \leq |_{\mathcal{A}_{\xi}}$  over  $\mathcal{A}_{\xi}$ , where  $R|_{A}$  restricts the binary relation R to elements from A and  $\leq$  is the standard order on natural numbers.

Since the JMM requires initialisation events (i.e. *Alloc*) to be ordered before the threads' initial events, I introduce the (total) execution order  $\leq_{e_0}^{\xi}$  on  $\mathcal{A}_{\xi}$ :

$$\alpha \leq_{\mathrm{eo}}^{\xi} \alpha' \longleftrightarrow (if \, init_{\xi} \, \alpha \, then \, \neg init_{\xi} \, \alpha' \vee \alpha \leq^{\xi} \alpha' \, else \, \neg init_{\xi} \, \alpha' \wedge \alpha \leq^{\xi} \alpha')$$

(2)

where  $init_{\xi} \alpha$  predicates that  $\alpha$  is an allocation event in  $\xi$ , i.e.,  $\xi_{[\alpha]} = (\_, Alloc\_\_)$ .

The program order  $\leq_{\mathrm{po}}^{\xi}$  restricts  $\leq_{\mathrm{eo}}^{\xi}$  to events of the same thread. The synchronisation order  $\leq_{\mathrm{so}}^{\xi}$  restricts  $\leq_{\mathrm{eo}}^{\xi}$  to synchronisation events. Synchronisation events are allocations (Alloc), reads from and writes to volatile locations, locking (Lock) and unlocking (Unlock), thread spawns (Spawn) and joins (Join), thread start (Start) and finish events (Start), and the interruption events Start and Start Start restricts Start to release-acquire pairs of events. (Start) is a release-acquire pair (notation Start) definition in Fig. 12) iff

- $\alpha$  unlocks a monitor and  $\alpha'$  locks the same monitor,

- $\alpha$  spawns a thread whose start action is  $\alpha'$ ,

- $\alpha$  is the finish event of the thread on which  $\alpha'$  joins,

```

(t, Unlock a) \longrightarrow (t', Lock a)

(t, Alloc \ a \ T) \longrightarrow (t', Start)

(t, Spawn t' \_) \rightarrow (t', Start)

(t, \mathbf{Write}\ (a, l)\ v) \longrightarrow (t', \mathbf{Read}\ (a, l)\ v')

(t, \mathbf{Finish}) \longrightarrow (t', \mathbf{Join}\ t)

(t, Alloc \ a' \ T) \longrightarrow (t', Read \ (a, l') \ v) \quad \text{if } l' \in memb \ T

(t, Intr t'') \longrightarrow (t', Intrd t'')

```

Fig. 12: Release-acquire pairs

- $\alpha$  interrupts a thread t and  $\alpha'$  observes that t has been interrupted,

- $\alpha$  is an allocation event and  $\alpha'$  is a thread start event, <sup>14</sup> or

- $\alpha$  writes to a location that  $\alpha'$  reads. <sup>15</sup>

The happens-before order  $\leq_{\mathrm{hb}}^{\xi}$  is the transitive closure of  $\leq_{\mathrm{po}}^{\xi}$  and  $\leq_{\mathrm{sw}}^{\xi}$ . This concludes the construction of orders from traces.

2.4.3. Well-formed Executions. An execution  $(\xi, ws)$  consists of a trace  $\xi$  and a writeseen function ws that assigns to every read event in  $\mathcal{R}_{\xi}$  the write event it sees. This yields the JMM notion of an execution [Gosling et al. 2005, §17.4.6] as  $(\mathcal{E}, \mathcal{A}, \leq_{po}, \leq_{so}, ws, \mathbf{vw}, \leq_{sw}, \leq_{hb}).$

An execution is well-formed (written  $(\xi, ws)\sqrt{\ }$ ) iff every thread has a thread start event that  $\preceq^{\xi}$ -precedes its other events except for allocation events (denoted  $\xi \sqrt{_{\text{Start}}}$ ) and for all read events  $\alpha \in \mathcal{R}$  to some location (a, l),

```

(W1) ws \ \alpha writes to (a, l), i.e., ws \ \alpha \in \mathcal{W} and (a, l) \in locs \ (ws \ \alpha),

```

(W2)  $\alpha$  reads the value vw (ws  $\alpha$ ) (a, l),

(W3)  $\alpha \not\leq_{\text{hb}} ws \alpha$ ,

(W4) for all write events  $\beta$  to (a,l), if  $ws \ \alpha \leq_{\mathrm{hb}} \beta \leq_{\mathrm{hb}} \alpha$ , then  $\beta = ws \ \alpha$ , and (W5) if  $\alpha$  is a volatile read, then  $\alpha \not \leq_{\mathrm{so}} ws \ \alpha$  and for all write events  $\beta$  to (a,l), if  $ws \ \alpha \leq_{so} \beta \leq_{so} \alpha$ , then  $\beta = ws \ \alpha$ .

$\xi$  is well-formed iff  $(\xi, ws)\sqrt{\text{ for some } ws.}$

These conditions correspond to the JMM well-formedness conditions 1 (each read sees a write to the same location), 4 ( $\leq_{

m hb}$  consistency) and 5 ( $\leq_{

m so}$  consistency for volatiles) in [Gosling et al. 2005, §17.4.7].  $(\xi, ws)$  meets conditions 2  $(\leq_{bb}$  is a partial order) and 3 (intra-thread consistency) by construction. Moreover, layer 4 of the single-threaded semantics ensures that all traces  $\xi \in \mathcal{E}$  satisfy  $\xi \sqrt{_{\text{Start}}}$ . Note that conditions W3 and W4 do not imply condition W5, because  $\leq_{\text{hb}}$  contains

only  $\leq_{sw}$ , but not  $\leq_{so}$ . For example, the execution in Fig. 4 satisfies all well-formedness conditions except W5. Remember that it is  $\leq_{so}$  that forces all threads to agree on a global order of synchronisation events.

Reconsider the program in Fig. 5. Since there is a trace for every possible value (cf.  $\S 2.2$ ),  $\mathcal{E}$  contains a trace

```

\xi = [\dots, (t_1, Read \times 1), (t_2, Read \times 1), (t_1, Write \times 1), (t_2, Write \times 1), \dots]

```

The omitted events include those necessary to allocate and to spawn the threads – similar to the example in §2.3, but they do not constrain the write-seen function on the events mentioned. In particular, each read may see the respective write, because they may happen concurrently. Therefore, the execution in Fig. 5b is well-formed.

$<sup>^{14}</sup>$ There has been some unclarity whether allocations of objects without volatile fields should synchronise with thread start events [Aspinall and Ševčík 2007a, 2007b]. I assume that all allocations synchronise with Start events, because the DRF guarantee (§3) and consistency (§4) rely on this.

$<sup>^{15}\</sup>mathrm{I}$  do not need to restrict writes and reads to volatiles explicitly like the JMM does [Gosling et al. 2005, §17.4.4], because the synchronisation order already imposes this.

2.4.4. Legal executions. Still, the JMM disallows the execution by imposing additional legality constraints. As the following presentation is very technical, readers unfamiliar with the JMM may want to first look at [Aspinall and Ševčík 2007a; Huisman and Petri 2007] for a warm-up.